System Architecture

Static partition locks validated switching, routing and packet logic, while dynamic partition supports custom encryption, authentication and data-processing blocks.

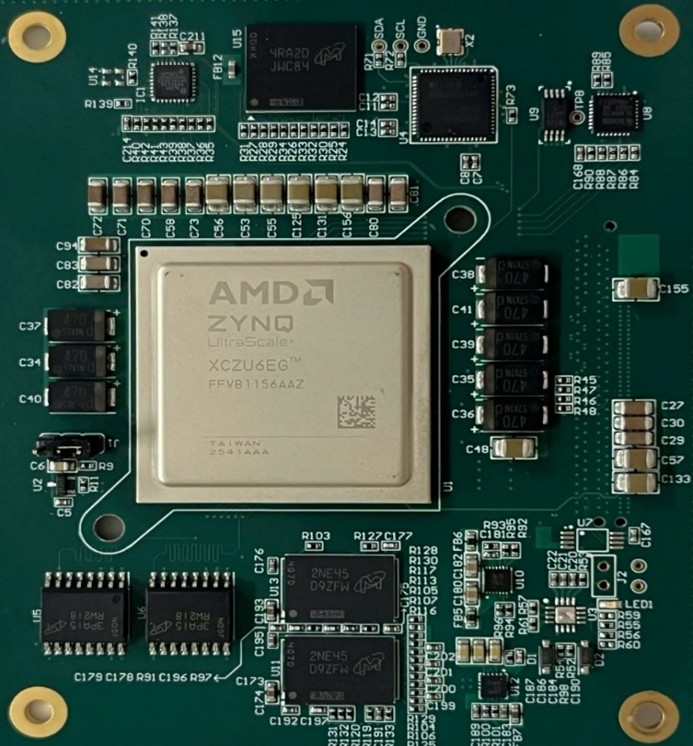

SOM-NetFPGA-6EG-2G is built around AMD Zynq UltraScale+ MPSoC XCZU6EG, combining multi-core ARM processing with FPGA acceleration in one compact architecture. It is designed for high-performance embedded products that need stable deployment, security and flexible feature scaling.

Static partition locks validated switching, routing and packet logic, while dynamic partition supports custom encryption, authentication and data-processing blocks.

Embedded Linux BSP with U-Boot boot modes from QSPI and eMMC, including reference device tree, drivers, root filesystem template and Vivado assets.

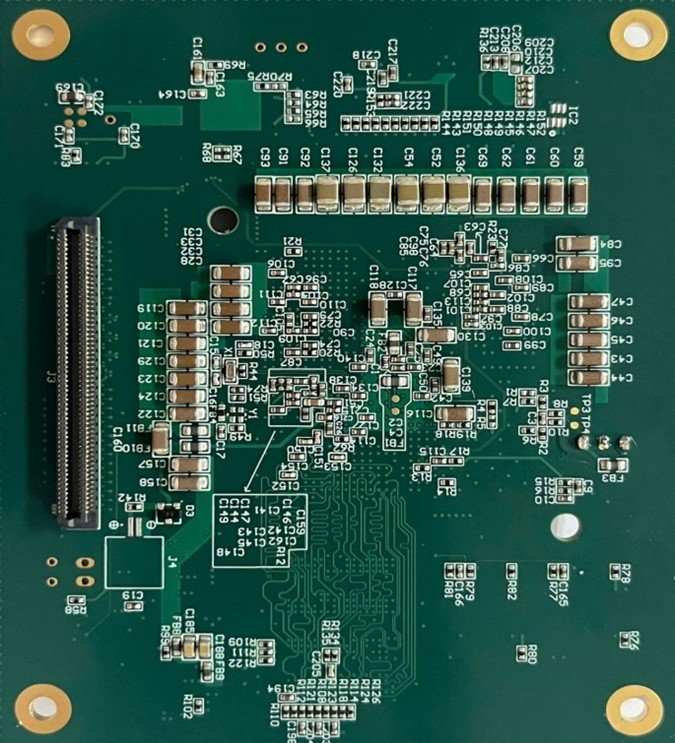

Industrial-grade design with firmware tests, vector tests and PCBA quality inspection to ensure consistency, traceability and long-term deployment support.

| SoC | AMD Zynq UltraScale+ MPSoC XCZU6EG-2FFVB1156 with quad ARM Cortex-A53, dual Cortex-R5 and Mali-400 GPU. |

|---|---|

| Memory | DDR4 options from 2 GB to 4 GB (single or dual rank depending on product configuration). |

| Boot & Storage | QSPI Flash for FSBL/bitstream boot and eMMC (8 GB to 16 GB) for Linux system and application data. |

| Connectivity | UART, I2C, SPI, GPIO, 1GbE or SFP networking, plus expansion options such as PCIe and high-speed connector lanes. |

| Target Applications | Firewall, SD-WAN, industrial controller, AI edge accelerator, image processing and telecom workloads. |

Supports DDR4, eMMC and Flash options, with optional PHY, SFP or PCIe components integrated per application requirement.

Manufacturing flow includes visual, electrical, functional and software validation checks before shipment.

Long lifecycle product policy for enterprise projects that require sustained maintenance and supply continuity.

Standard kit starts with XCZU6EG + 2 GB DDR4 + 16 GB eMMC + QSPI Flash, with evaluation board options for development.

Contact us for lead time, customization scope, hardware package and software handover details.